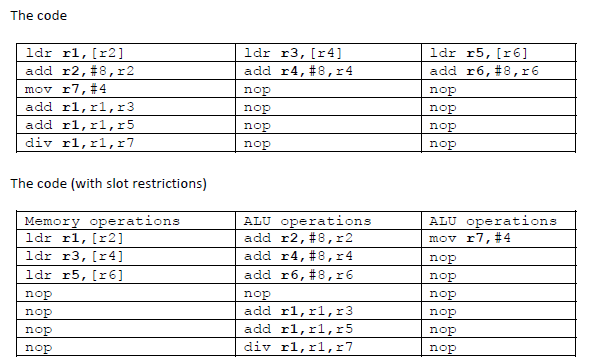

Demonstrate how a compiler might translate the following fragment of code into a form that can run on a VLIW processor that specifies three operations per instruction word (i.e., three instructions per bundle in Itanium terminology). You may perform instruction reordering. Assume that the latency for a load is three cycles and the latency for a multiply is two cycles (i.e., the load takes three cycles in total). Use a NOP whenever an instruction slot cannot be filled.

mov r7,#4

ldr r1,[r2]

ldr r3,[r4]

ldr r5,[r6]

add r1,r1,r3

add r1,r1,r5

div r1,r1,r7

add r2,#8,r2

add r4,#8,r4

add r6,#8,r6

Repeat the same exercise but assume that the VLIW processor can perform only one memory access operation

per cycle. Assume that the memory unit is fully pipelined; that is, it has a latency of three cycles but the next

memory operation can begin in the following cycle.

Computer Science & Information Technology

You might also like to view...

The most common hybrid system is based on the Diffie-Hellman key exchange, which is a method for exchanging private keys using public-key encryption.

Answer the following statement true (T) or false (F)

Computer Science & Information Technology

?Data ______ tools can take raw data and immediately provide a rich visual image.

Fill in the blank(s) with the appropriate word(s).

Computer Science & Information Technology